# **GESTION CLAVIER MATRICIEL 16 TOUCHES**

# PRESENTATION GENERALE:

# Principe du clavier matriciel :

Un clavier matriciel (ici 16 touches) dispose uniquement de 8 broches pour la gestion de ses touches. L'organisation est de 4 colonnes et 4 lignes. Les lignes ont un état de repos imposé (ici l'état bas).

# Schéma de présentation :

#### La détection des touches

Il faut balayer les colonnes une à une par un état haut. Ainsi dès lors qu'une touche est pressée, l'état de la colonne est transmit sur la ligne. Nous pouvons ainsi détecter un état haut. Pour déterminer la touche pressée, il faut se synchroniser avec le signal envoyé sur les colonnes.

### SOMMAIRE

| SOMMAIRE                                    | 1 |

|---------------------------------------------|---|

| PREMIERE PARTIE : ANALYSE                   | 2 |

| 1)-Generation du signal pour les colonnes : |   |

| 1) - GENERATION DU SIGNAL POUR LES COLONNES |   |

| 1-2)- Décodage :                            | 2 |

| 2)- Decodage et affichage :                 | 3 |

| 2-1)- Décodage des touches :                | 3 |

| 2-2)- Transcodage vers 7 segments :         | 4 |

| 3)- SCHEMA FONCTIONNEL COMPLET :            | 5 |

| DEUXIEME PARTIE : CODAGE                    | 5 |

| 1)- Les differents signaux :                | 5 |

| 2)- L'ENTITE:                               |   |

| 3)- L'ARCHITECTURE :                        |   |

Lycée Jules Ferry 1 VHDL

# Première Partie : Analyse

# 1)-Génération du signal pour les colonnes :

Nous disposons de quatre colonnes donc les combinaisons à générer sont les suivantes : 1000, 0100, 0010, 0001. Pour ce faire, il nous faut un compteur et un décodeur.

### 1-1)- Le compteur :

### a)- Modulo:

Disposant de quatre combinaisons,  $2^n = 4 \rightarrow n = 2$ . Il nous faut donc un compteur 2 bits.

# b)- Horloge:

Le signal d'horloge détermine la vitesse de balayage des colonnes. Elle est choisit suffisamment élevée (par rapport en l'enchaînement de deux touches pressées).

| CLK      | a1 | <b>a</b> 0 |

|----------|----|------------|

| <b>↑</b> | 0  | 0          |

| <b>1</b> | 0  | 1          |

| <b>1</b> | 1  | 0          |

| <b>1</b> | 1  | 1          |

### 1-2)- Décodage :

Il nous faut modifier le code précédent pour générer les quatre combinaisons nécessaires pour nos colonnes.

| a1 | <b>a</b> 0 | <b>C3</b> | <b>C2</b> | <b>C1</b> | C0 |

|----|------------|-----------|-----------|-----------|----|

| 0  | 0          | 1         | 0         | 0         | 0  |

| 0  | 1          | 0         | 1         | 0         | 0  |

| 1  | 0          | 0         | 0         | 1         | 0  |

| 1  | 1          | 0         | 0         | 0         | 1  |

Le signal « a1a0 » va nous permettre d'assurer la synchronisation pour le décodage des touches.

Lycée Jules Ferry 2 VHDL

# 2) - Décodage et affichage :

# 2-1)- Décodage des touches :

Compte tenu des explications précédentes nous pouvons établir la table de vérité suivante.

| <b>a</b> 0 | a1 | 13 | 12 | 11 | 10 | touche pressée |

|------------|----|----|----|----|----|----------------|

| 0          | 0  | 1  | 0  | 0  | 0  | 1              |

| 0          | 0  | 0  | 1  | 0  | 0  | 4              |

| 0          | 0  | 0  | 0  | 1  | 0  | 7              |

| 0          | 0  | 0  | 0  | 0  | 1  | A              |

| 0          | 1  | 1  | 0  | 0  | 0  | 2              |

| 0          | 1  | 0  | 1  | 0  | 0  | 5              |

| 0          | 1  | 0  | 0  | 1  | 0  | 8              |

| 0          | 1  | 0  | 0  | 0  | 1  | 0              |

| 1          | 0  | 1  | 0  | 0  | 0  | 3              |

| 1          | 0  | 0  | 1  | 0  | 0  | 6              |

| 1          | 0  | 0  | 0  | 1  | 0  | 9              |

| 1          | 0  | 0  | 0  | 0  | 1  | В              |

| 1          | 1  | 1  | 0  | 0  | 0  | F              |

| 1          | 1  | 0  | 1  | 0  | 0  | E              |

| 1          | 1  | 0  | 0  | 1  | 0  | D              |

| 1          | 1  | 0  | 0  | 0  | 1  | C              |

Lycée Jules Ferry 3 VHDL

# 2-2) Transcodage vers 7 segments :

Lorsque la touche est pressée il faut donc afficher sa valeur sur l'afficheur 7 segments. Nous considérons que les segments sont allumés par un état haut.

Nous en déduisons le tableau suivant :

| Entrées           | Sorties |   |   |   |   |   | \$ | Valeur affichée |     |

|-------------------|---------|---|---|---|---|---|----|-----------------|-----|

| a1 a0 13 12 11 10 | g       | f | e | d | c | b | a  | Ψ               |     |

| \$08              | 0       | 0 | 0 | 0 | 1 | 1 | 0  | 06              | - 1 |

| \$04              | 1       | 1 | 0 | 0 | 1 | 1 | 0  | 66              | 4   |

| \$02              | 0       | 0 | 0 | 0 | 1 | 1 | 1  | 07              | 7   |

| \$01              | 0       | 1 | 1 | 1 | 1 | 1 | 1  | 3F              | 8   |

| \$18              | 1       | 0 | 1 | 1 | 0 | 1 | 1  | 5B              | 5   |

| \$14              | 1       | 1 | 0 | 1 | 1 | 0 | 1  | 6D              | 5   |

| \$12              | 1       | 1 | 1 | 1 | 1 | 1 | 1  | <b>7</b> F      | 8   |

| \$11              | 1       | 1 | 1 | 0 | 0 | 0 | 1  | 71              | 0   |

| \$28              | 1       | 0 | 0 | 1 | 1 | 1 | 1  | <b>4</b> F      | 3   |

| \$24              | 1       | 1 | 1 | 1 | 1 | 0 | 1  | <b>7D</b>       | 8   |

| \$22              | 1       | 1 | 0 | 1 | 1 | 1 | 1  | 6F              | 9   |

| \$21              | 1       | 1 | 1 | 1 | 0 | 0 | 1  | 79              | ь   |

| \$38              | 1       | 1 | 1 | 0 | 1 | 1 | 1  | 77              | ۶   |

| \$34              | 1       | 1 | 1 | 1 | 1 | 0 | 0  | 7C              | 8   |

| \$32              | 0       | 1 | 1 | 1 | 0 | 0 | 1  | 39              | 8   |

| \$31              | 1       | 0 | 1 | 1 | 1 | 1 | 0  | 5E              | 0   |

Lycée Jules Ferry 4 VHDL

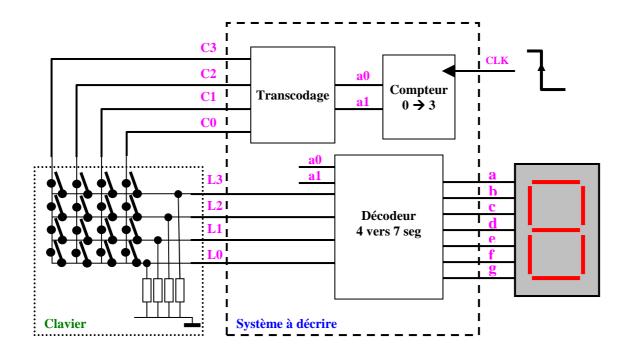

### 3) - Schéma fonctionnel complet:

# Deuxième Partie : Codage

Au niveau du codage, il nous faut déterminer l'entité et l'architecture. L'entité et obtenue facilement par la partie pointillée qui délimite le système. Pour l'architecture, il convient de décrire les différents composants à l'intérieur des pointillés.

#### 1) - LES DIFFERENTS SIGNAUX:

### • Définis dans l'entité :

- > Entrées :

- CLK : signal d'horloge (std\_logic)

- L3, L2, L1, L0 : signal pour décodage des lignes (std\_logic\_vector3downto0)

- > Sorties:

- C3, C2, C1, C0 : signal de balayage (std\_logic\_vector3downto0)

- gfedcba : signal contrôle afficheur (std\_logic\_vector6downto0)

#### • Définis dans l'architecture :

- ➤ Signal interne :

- a1a0 : Signal du compteur  $0 \rightarrow 3$

### 2) - L'ENTITE :

## 3) - L'ARCHITECTURE :

Il faut donc réaliser la descritpion d'un compteur 2 bits, un décodeur 2 vers 4 (balayage colonnes) et enfin un décodeur 6 vers 7 segments.

```

Architecture equa of clavier is

Signal a1a0 : std_logic_vector(1 downto 0);

Begin

-- compteur

-- decodeur 2 vers 4

-- decodeur 6 vers 7

End equa ;

```